Le prochain processeur hautes performances de la Nasa ne sera pas un Core de 12e génération. Ni une puce ARM d’iPhone. Et certainement pas davantage une puce PowerPC, comme dans Perseverance ou le JWST. Non, la future puce du High-Performance Spaceflight Computing de l’agence américaine, qui devrait déployer « cent fois plus de puissance que les ordinateurs spatiaux actuels » aura des cœurs basés sur une toute autre microarchitecture appelée RISC V.

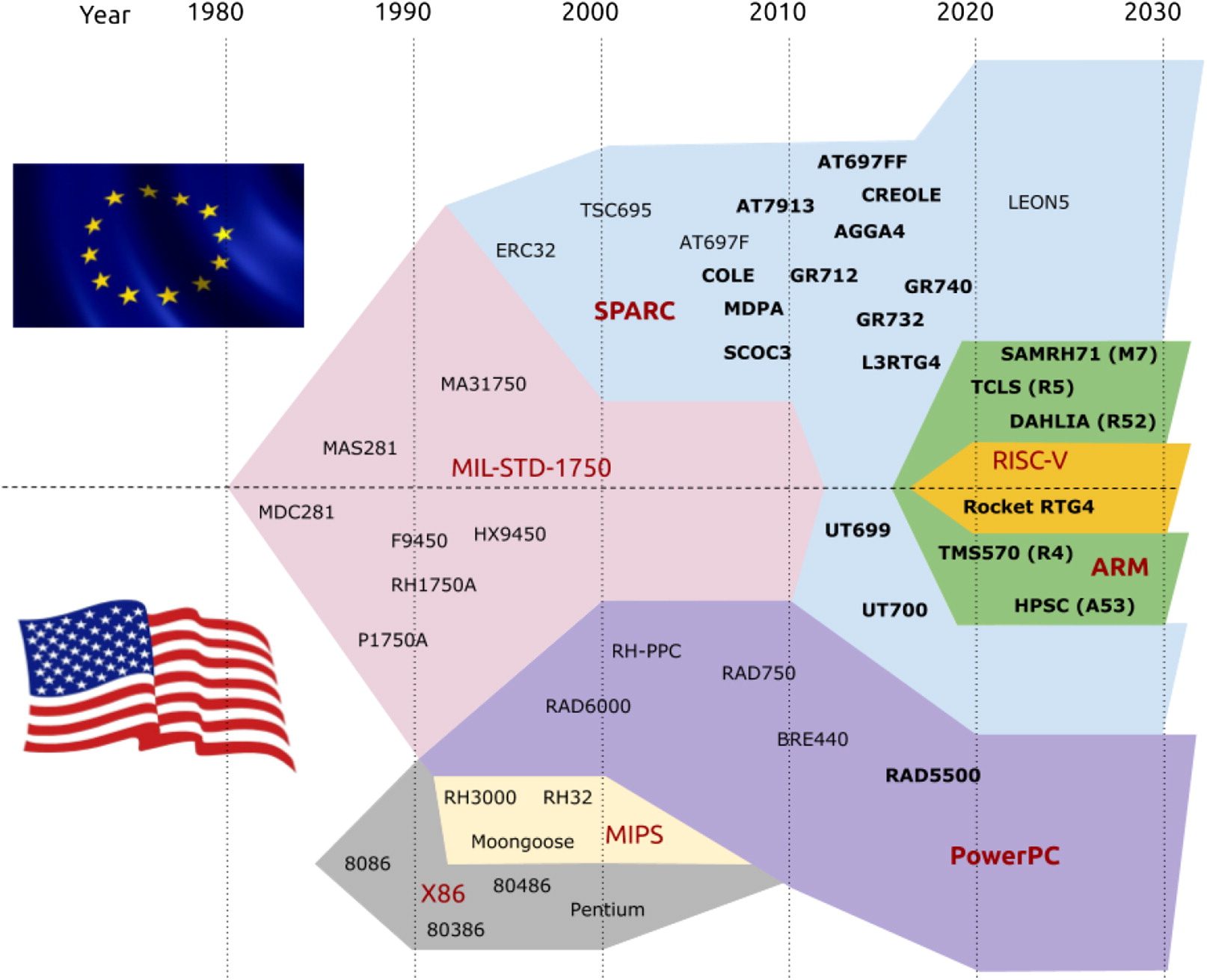

Même son de cloche dans notre belle Europe. RISC V a non seulement été sélectionnée comme successeur du SPARC actuellement usage, mais en plus le premier FPGA programmé en utilisant cette microarchitecture vole déjà dans l’espace depuis maintenant trois semaines. Ce qui veut dire que dans quelques années, toutes les puces assurant les missions critiques des deux plus grandes agences spatiales du monde fonctionneront sur les mêmes jeux d’instructions.

Pour comprendre l’importance de ces nouvelles, il faut comprendre (un peu) ce qu’est RISC V et ce que cette architecture porte en elle. Il faut aussi connaître (un peu là aussi) les puces spatiales actuelles, ainsi que la spécificité de contraintes qu’elles subissent. Et pour cela, il faut aussi comprendre (un tout petit peu, promis !) le contexte actuel de ces architectures.

On y va ? Prêt pour votre premier décollage ? Destination : vers (presque) l’infini et l’au-delà. Un futur de l’informatique spatiale qui porte peut-être avec lui, qui sait, de celui de l’informatique terrestre.

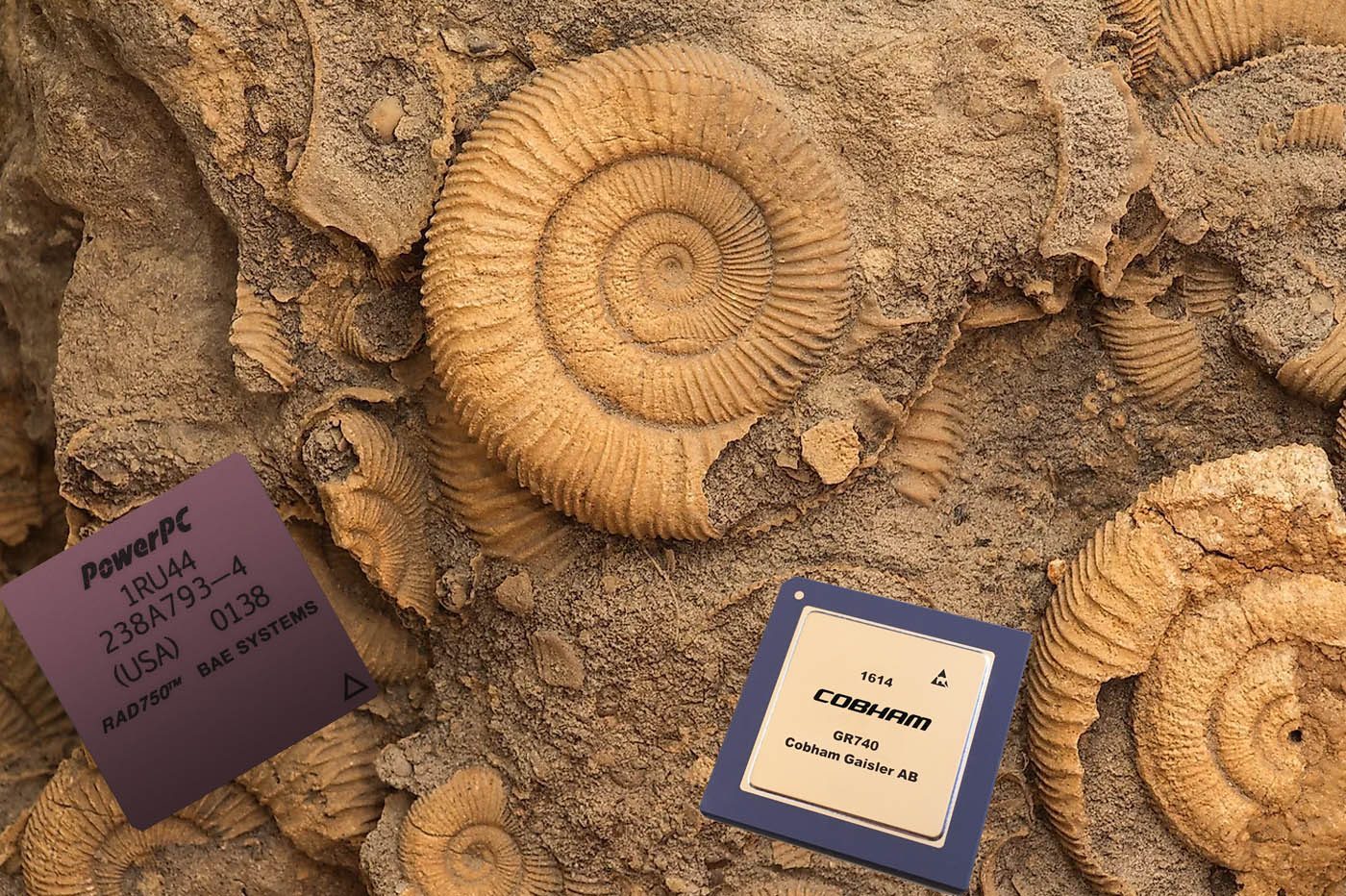

Les processeurs spatiaux actuels sont des fossiles

Personne n’entend les processeurs spatiaux crier. Dans cet environnement hostile, les morceaux de silicium sont mis à rude épreuve. Dépourvus de la puissante protection électromagnétique de notre planète, les rayonnements cosmiques peuvent perturber les puces et faire « sauter » les bits. Aussi anodin que cela puisse paraître sur le papier, cette transformation d’un « 0 » en « 1 » (et vice-versa) appelé « flip » de bit, peut mettre à plat n’importe quel système informatique classique. Mais pas les puces employées par les différentes agences spatiales. Indépendamment de leur microarchitectures, ces puces sont toutes blindées contre les radiations d’une part, et conçues pour la redondance et la sécurité (matérielle et logicielle) d’autre part.*

Côté américain, le processeur de choix des missions spatiales est le RAD750. Véritable « cheval de trait » des deux dernières décennies, cette puce qui pilote aujourd’hui le rover Perseverance ou encore le James Webb Space Telecospe est basée sur le PowerPC qui animait… le tout premier iMac ! Puissant à son lancement, ce processeur cadencé à 233 MHz a fait ses preuves… mais il limite énormément les capacités de calcul embarqué.

Lire aussi : Comment un processeur Intel Atom s’est retrouvé sur Mars

Le programme spatial européen a, lui, sa propre architecture de processeur souverain, appelé LEON. Basé sur une technologie encore plus exotique baptisée SPARC -le fer de lance des puces Sun Microsystems- LEON est employée dans de nombreuses puces, dont le fleuron est le GR740. Cette puce basée sur quatre coeurs LEON4 existe dans une version cadencée à… 250 MHz. Robuste ? Oui. Puissante ? Pas vraiment ! Taillée pour le futur ? Aboslument pas. Car LEON est, comme le PowerPC, basée sur une version 32 bits de l’architecture, empêchant une montée en puissance. Et plus gênant que pour PowerPC : l’architecture SPARC a été abandonnée, Sun et Fujitsu ayant jeté l’éponge.

Les puces spatiales actuelles de la NASA et de l’ESA sont donc bien fiables et éprouvées. Et elles s’appuient sur des chaînes d’approvisionnement et logicielles robustes, et souveraines. Mais elles sont toutes deux mourantes, avec peu ou pas d’industriels investis dessus, ce qui empêche les effets d’échelle. Et interdit de regarder vers le futur.

Or, le renouveau spatial a un énorme besoin de puissance de calcul.

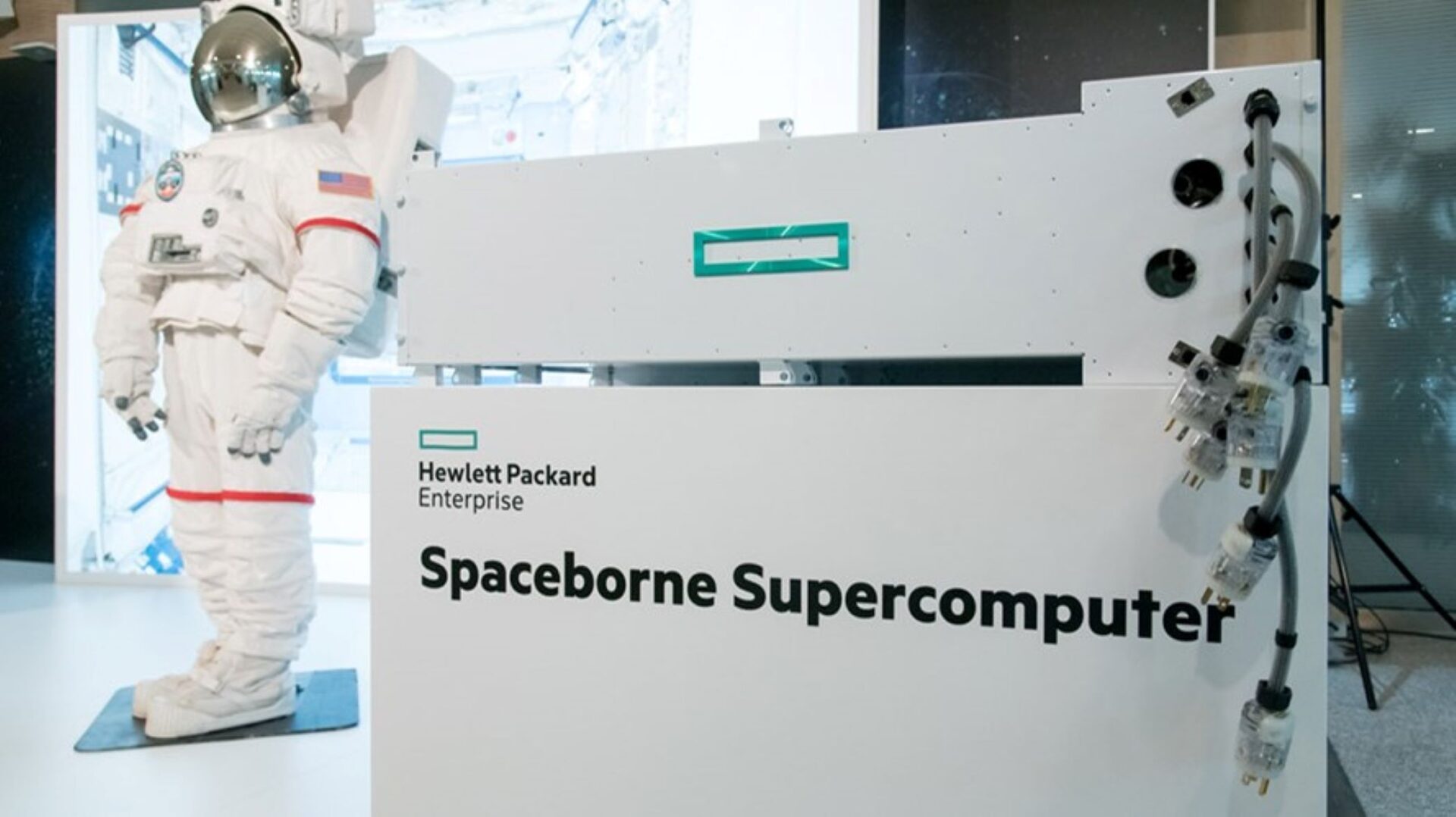

Le futur de la conquête spatiale a soif de puissance

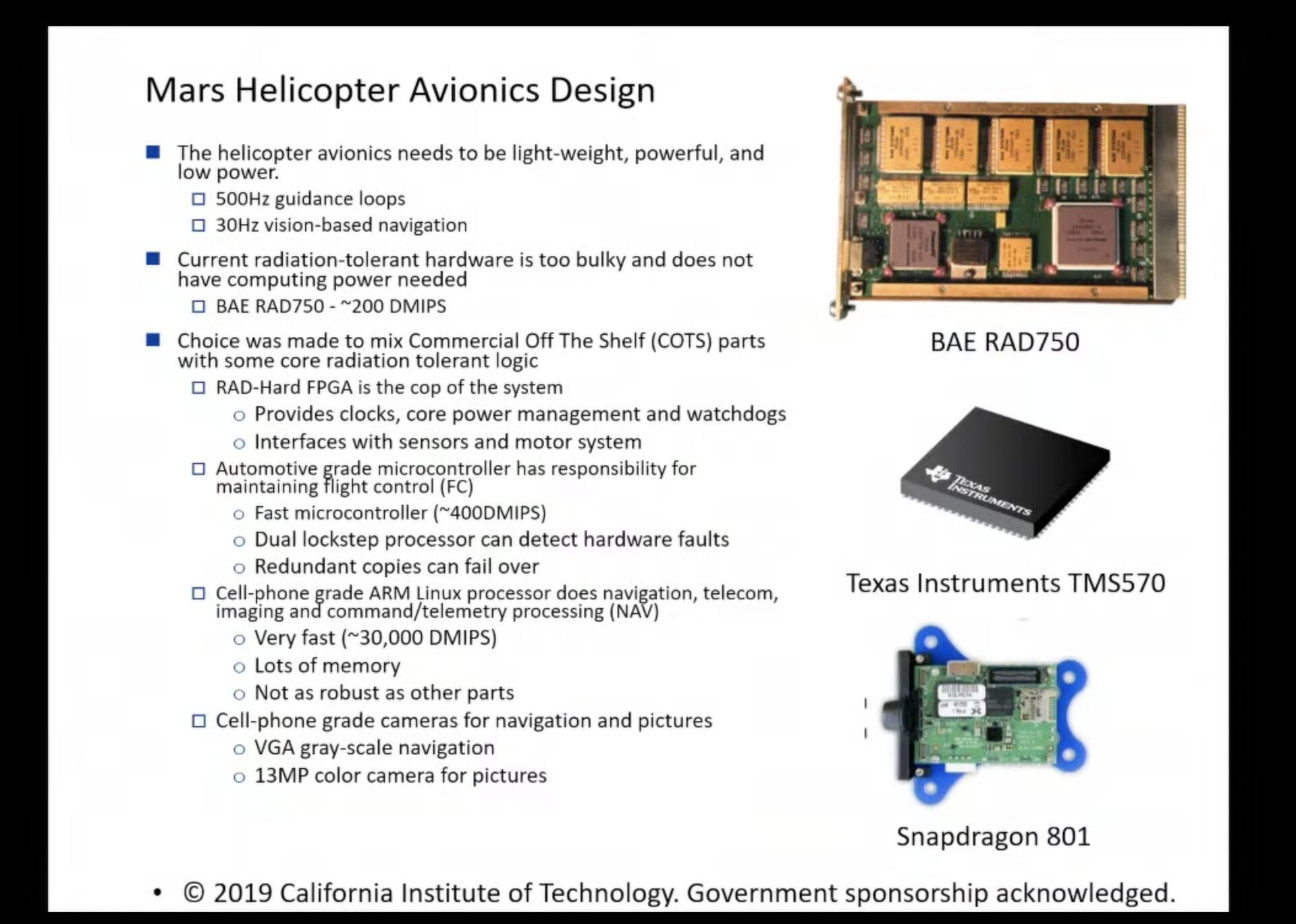

Le monde de l’espace est en plein remue-ménage. Il y a l’ESA qui teste un VPU d’Intel achetée sur étagère dans un micro satellite météo. Il y a aussi HPE, qui a testé et validé avec la NASA un petit supercalculateur spatial dans la station internationale. Ou encore le drone martien Ingenuity, qui vole de manière quasi autonome sur la planète rouge grâce à une vieille puce de smartphone. Ces trois projets font appel à des composants « terrestres » qui ne sont pas blindées contre les radiations. C’est pourquoi ils n’animent que des projets expérimentaux, voire secondaires dans le cas d’Ingenuity. Mais ils sont la preuve que l’industrie spatiale est à la recherche de plus de puissance.

Lire aussi : Comment les puces VPU vont révolutionner la conquête spatiale

Pour vous donner un ordre d’idée du différentiel de puissance entre les puces de votre ordinateur ou votre smartphone et les RAD750 et autre LEON 4, considérez Ingenuity. Le drone de la NASA est arrivé sur Mars en même temps que son grand frère, le rover Perseverance. Alors que le plus puissant des processeurs de ce dernier est un bon vieux RAD 750, Ingenuity intègre un Snapdragon 801. Ce SoC annoncé en 2014 est une puce ARM quad-core gravée en 28 nm. Avec une partie CPU pouvant aller jusqu’à 2,3 GHz et un GPU Adreno 330 allant jusqu’à 578 MHz, cette vieille puce qui équipait les Motorola Moto X (2nd Gen) et Sony Xperia Z3 est complètement dépassée par le moindre processeur milieu de gamme actuel. Pourtant, sa puissance est déjà suffisante pour permettre à Ingenuity de voler de manière autonome sur Mars. Et s’avère dix fois plus puissante que la totalité des puces embarquées par le rover Perseverance !

Entre les besoins de pilotage autonome, les limites des protocoles spatiaux de transmissions de données, la montée en définition et résolution des instruments scientifiques (capteurs d’image, etc.), le monde de l’espace doit changer de braquet. Mais alors pourquoi ne pas simplement utiliser ce qui fonctionne déjà sur terre comme la puce pour smartphone de notre exemple et l’adapter à l’espace ?

x86 et ARM n’avaient aucune chance

Deux microarchitectures de puces régissent notre monde : x86 et ARM. Quand vous allumez votre PC, quand vous demandez à Netflix de vous envoyer une vidéo, aussi bien votre ordinateur (non Mac) que le centre de données distant sont généralement basés sur des puces Intel ou AMD. Des processeurs qui sont basés sur une microarchitecture qui a désormais 40 ans, appelée x86.

Que vous lanciez Disney+ sur votre TV connectée, que vous lisez sur votre smartphone ou que vous consultiez l’ordinateur de bord de votre voiture, ce sont alors des puces utilisant la microarchitecture ARM qui s’animent. Cette dernière architecture, grâce à son système de licence, a de plus le vent en poupe avec une montée en puissance dans de nombreux marchés – regardez la bascule d’Apple vers les puces M1 et M2.

Ces deux comparses que sont x86 et ARM dominent le monde terrestre. L’une comme l’autre a ses forces : à x86 une énorme compatibilité logicielle et a une grande capacité de montée en puissance. ARM le meilleur rapport performances/watt et toute entreprise qui paye une licence et a les compétences peut se concocter une puce maison. De plus, les deux architectures sont à la source de milliards de puces produites chaque année – de quoi profiter de vrais effets d’échelle. Pourtant, elles n’avaient (absolument) aucune chance d’être choisies par les autorités spatiales.

Lire aussi : Avec IFS, les usines d’Intel sont au coeur de sa nouvelle stratégie

Pas à cause de leurs structures – encore que le rapport performance/watt du x86 ne soit pas à son avantage ces derniers temps – mais pour une cause bien plus politique : la souveraineté. Même si Intel peut arguer que son service IFS permet désormais de concevoir des puces avec des bouts CPU en x86, la totalité de la propriété intellectuelle de x86 appartient à Intel (et à AMD dans une certaine mesure).

Quant à ARM, même si l’entreprise britannique revendique 500 clients et permet à certains comme Apple de concevoir leurs propres cœurs CPU, là encore les instructions sont la propriété de l’entreprise. Un géant comme Qualcomm, qui l’un des plus gros clients d’ARM en fait d’ailleurs actuellement les frais. Autant la NASA que l’ESA ont besoin de maîtriser leurs technologies et ne pas peuvent pas être à la merci de l’histoire ou des velléités de telle ou telle entreprise.

Et c’est là qu’intervient RISC V.

RISC V : ouvert, collaboratif et (potentiellement) souverain

S’il est difficile de s’en rendre compte au quotidien, les architectures de nos puces sont, en fait, soumises au bon vouloir de quasi-monopoles. En contraste, RISC V n’appartient à personne. Issu d’un projet universitaire pour apprendre aux étudiants à concevoir des puces de type RISC, le programme a été placé en 2020 sous le contrôle d’une fondation de droit suisse. Cette manœuvre, qui s’est opérée après que les USA ont échoué à empêcher ARM d’octroyer une licence à Huawei, a mis le jeu d’instructions à l’abri de toute ingérence gouvernementale.

Lire aussi : RISC-V, le rival d’ARM, va se doter de son premier GPU (et c’est loin d’être un détail)

Ce qui fait de RISC V la seule microarchitecture ouverte et coopérative. Qui que vous soyez, vous pouvez apprendre comment manipuler les instructions, concevoir votre propre cœur processeur. Et vendre ce savoir-faire en faisant votre propriété de l’agencement des transistors ou de la structure des cœurs. Sans jamais pouvoir empêcher les autres de travailler avec ces mêmes instructions. Du côté de la gouvernance, de nombreuses entreprises influent sur le développement des différents jeux d’instructions, à la manière de la façon dont est développé le noyau Linux.

Lire aussi : Pourquoi Apple se prépare à abandonner (partiellement) ARM pour RISC-V

Un cercle vertueux de l’innovation qui reprend quelques une des recettes du logiciel open source appliqué au matériel. Et qui a vu naître de nouveaux acteurs comme l’américain SiFive, qui s’est vu octroyer la semaine dernière un budget de 50 millions de dollars pour développer les cœurs CPU du futur.

SiFive, qui est aussi la première entreprise à avoir lancé un processeur RISC V facilement achetable par le grand public, a le vent en poupe – tellement qu’il y avait même des rumeurs de rachat par Intel l’an dernier. Les différents succès de cette entreprise lui ont donné du poids et de l’expérience qu’elle va utiliser pour développer des cœurs CPU éprouvés. L’avantage de l’ouverture de RISC V est ici : la NASA peut ainsi intervenir sur les cœurs et savoir comment ils fonctionnent. Et en cas de changement de fournisseur de propriété intellectuelle, la NASA peut plus aisément changer de fournisseur de technologie de cœur CPU.

Ce qui est intéressant dans le choix de RISC V par les deux agences spatiales, c’est que bien que des synergies bien plus fortes vont pouvoir se tisser entre la NASA et l’ESA. Alors que PowerPC était trop américain pour l’agence européenne, qui devait éviter d’être sous la coupe du continent ami, cette fois-ci l’ESA va pouvoir parler directement avec la NASA. Sur des jeux d’extensions ou des logiciels communs par exemple. Renforçant de facto le poids du spatial dans le développement de RISC V. Qui a encore beaucoup de chemin à faire.

RISC V doit murir, mais c’est bien lui le futur

Aux dizaines de millions de dollars qu’un nombre sans cesse croissant d’industriels injectent dans le développement des puces, s’ajoute un autre atout clé pour le futur de RISC V : le nombre, lui aussi croissant, de développeurs se tournant vers cette microarchitecture. Alors que de moins en moins de machines « terrestres » fonctionnent avec des puces PowerPC (sans parler du désert de SPARC), la communauté RISC V est en pleine explosion. En faisant de facto « l’architecture du futur », au moins pour l’espace. Et ce tant du point de vue des CPU, qui sont déjà produits industriellement, que des accélérateurs IA ou des GPU, tous deux en plein développement.

Ce qui ne veut pas dire qu’ARM (en pleine maturité) ou x86 (avec 4 décennies d’histoire et aux commandes de 90% des PC actuels) vont disparaître du jour au lendemain. De la même manière que la nature se nourrit de la diversité, il en va de même pour les technologies. Et celles des microarchitectures de processeur ne fait pas exception. D’autant que si les fondamentaux (RISC) et l’idée même de RISC V est ancienne, le standard RISC V est un bébé à côté de x86 et ARM.

Lire aussi : L’architecture RISC-V passe le cap de la gravure en 5 nm

Côté standard, il doit continuer de se développer. Autant d’un point de vue formel et théorique qu’en matière de nombre d’acteurs capable de s’en emparer. Il faut aussi que se consolident les différents écosystèmes logiciels autour de conception (design, validation, production) que de l’utilisation (systèmes d’exploitation, drivers, API, SDK, etc.) de ces puces.

Pour l’espace, il va aussi falloir choisir et développer les bons procédés de fabrication (finesse de gravure, matériaux, etc.) pour le blindage aux radiations, capital pour la survie des composants dans l’enfer électromagnétique de l’espace. Et si un design de puce peut prendre du temps, les qualifications matérielles et logicielles prennent souvent encore plus de temps.

Mais une chose est sûre : dans un contexte géopolitique actuel mouvementé qui rebat beaucoup de cartes, le statut ouvert et collaboratif de RISC V a été son arme principale pour des agences spatiales en quête de maîtrise de leur futur et de leur souveraineté.

👉🏻 Suivez l’actualité tech en temps réel : ajoutez 01net à vos sources sur Google, et abonnez-vous à notre canal WhatsApp.