TSMC n’en peut plus de courir en tête. Alors qu’elle est la seule entreprise à fournir du 5 nm en masse, surtout à Apple dans un premier temps, la firme taïwanaise a annoncé que des avancées de R&D significatives récentes lui permettront de lancer la production « à risque » de puces en 2 nm dès 2023 et que la production en masse sera prête dès 2024.

C’est la qualité et la finesse de gravure de TSMC qui lui permet d’attirer des clients comme AMD, Apple, Qualcomm, etc., et les enjeux de la miniaturisation sont de plus en plus importants à mesure que tous les produits du quotidien s’équipent en puces électroniques.

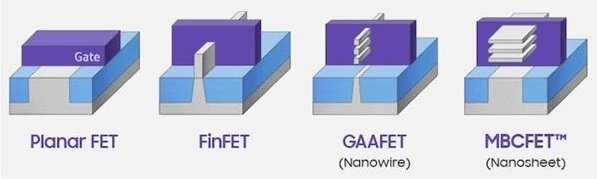

La production en 2 nm représentera un double succès pour TSMC puisque, outre la finesse record qu’elle semble la première à pouvoir atteindre, elle marquera aussi l’abandon de l’agencement des transistors selon la méthode FinFET.

En effet, le Taïwanais a mis la priorité sur la réduction de la taille minimal des transistors et la maîtrise de la gravure selon le nouveau procédé des ultraviolets extrêmes (EUV), au détriment de la complexité des portes des transistors – les « gates ».

Plusieurs analyses ont ainsi montré que la gravure en 10 nm d’Intel s’avère aussi dense en transistors que le 7 nm FinFET de TSMC.

Mais en perfectionnant sa gravure FinFET jusque dans ses derniers retranchements – le 3 nm devrait toujours utiliser ce procédé – TSMC a engrangé le cash suffisant et a donné le temps nécessaire à des équipes parallèles pour développer une gravure qui soit à la fois EUV, ultra fine (2 nm) et dont les transistors soient agencés de manière plus avancée.

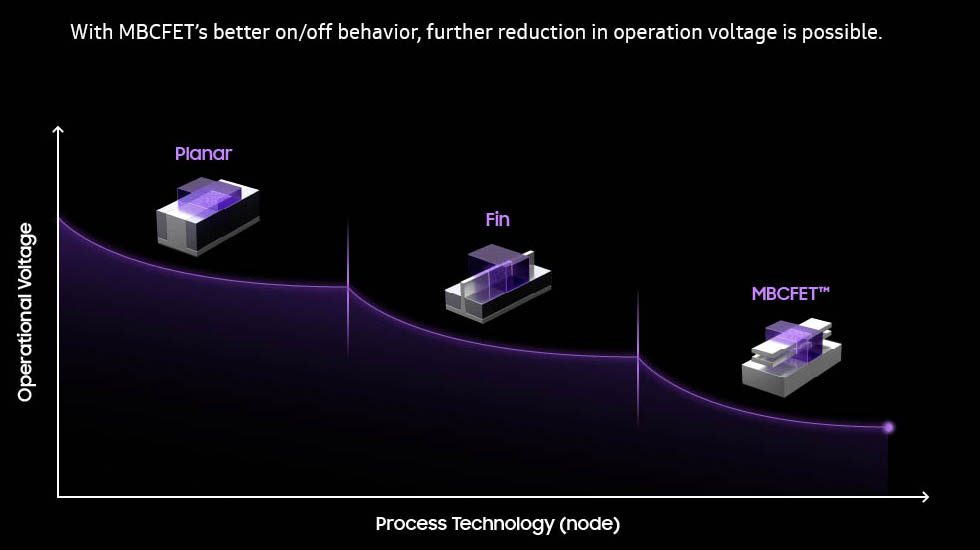

Le 2 nm sera donc l’occasion pour TSMC de passer du « simple » FinFET à une technologie proche du MBCFET (multi-bridge channel field effect transistor, ou transistor multicanal à effet de champ) appelé couramment « transistor 3D ».

L’appellation « MBCFET » appartient à Samsung et Intel développe une technologie similaire appelée « nano-ribbons » (nanorubans). Cela consiste à faire passer le signal par le biais de plusieurs nanofeuilles de matériau conducteur plutôt qu’un seul « nano-câble ».

Le double bénéfice de cette technique est de permettre de complexifier la puce et les connexions entre les différentes unités d’une puce tout en contenant encore mieux les problèmes de fuite énergétique liés à la réduction de la taille des transistors.

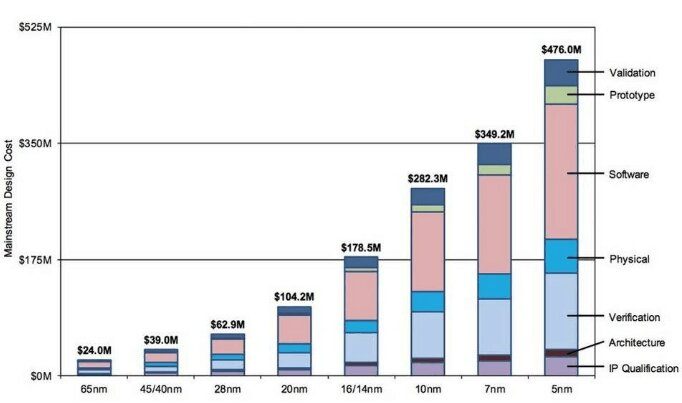

Selon toute vraisemblance, les premiers produits intégrant des puces 2 nm arriveront sur le marché à la fin de l’année 2023 au mieux, dès 2024 selon toute vraisemblance. Au vu de l’explosion des coûts de développement des technologies – le 5 nm a coûté 476 millions en R&D à mettre en place alors que le 14/16 nm n’avait coûté « que » 179 millions – ce procédé sera réservé aux puces qui seront à la fois volumiques et de pointe, tels les SoC des iPhone, par exemple.

Source : Gizchina

👉🏻 Suivez l’actualité tech en temps réel : ajoutez 01net à vos sources sur Google, et abonnez-vous à notre canal WhatsApp.