Si « intelligence artificielle » est devenue un mot valise utilisé à toutes les sauces, des briques technologiques sont pleinement opérationnelles et vont bientôt, en partie, piloter la conception des processeurs de Samsung.

Le coréen vient en effet d’annoncer utiliser les logiciels de l’américain Synopsys pour la conception de ses puces. Plus précisément, les derniers outils DSO.ai (Design Space Optimization AI) qui s’appuient sur l’IA pour optimiser l’agencement des milliards de transistors qui composent une puce.

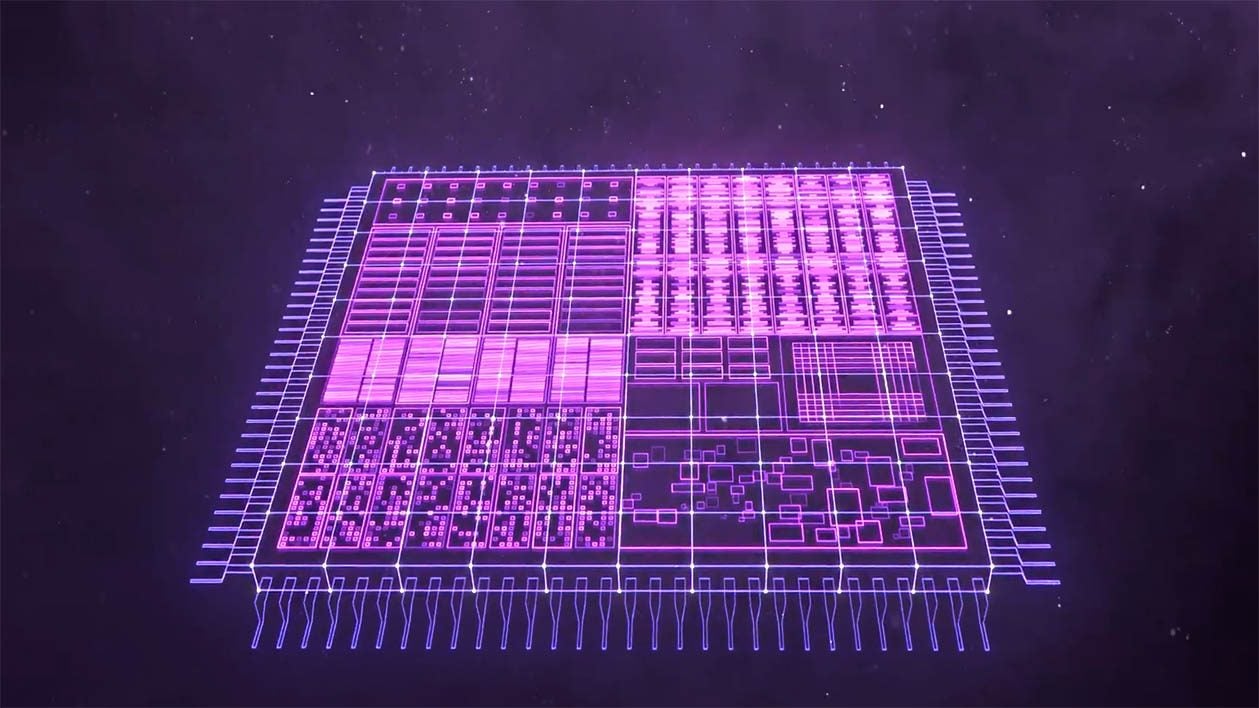

La tâche très spécifique d’entasser toutes ces unités sur quelques millimètres voire centimètres carrés s’appelle le « plan d’étage » (floor plan dans le jargon). Une étape d’une complexité phénoménale, les éléments (unités de calculs, mémoire cache, etc.) et connexions étant reliés entre-eux en trois dimensions afin de réduire l’empreinte spatiale de la puce. Une condition sine qua non pour que votre puce de smartphone ne prenne pas la moitié de la carte-mère !

Ce gigantesque labyrinthe doit être littéralement « plié » dans l’espace par des ingénieurs qui doivent faire des choix en matière de chauffe, d’éloignement des composants, de complexification de la puce, de limitation de la longueur interne des circuits, etc.

Dans cette tâche, si les outils de type EDA (electronic design automation, automatisation du design électronique) de Synopsys et de son concurrent Cadence ont toujours épaulé les concepteurs de puces, la brique de l’IA appelée « apprentissage machine » (machine learning) pourrait accélérer le temps de développement, tant l’étape du plan d’étage est chronophage.

À découvrir aussi en vidéo :

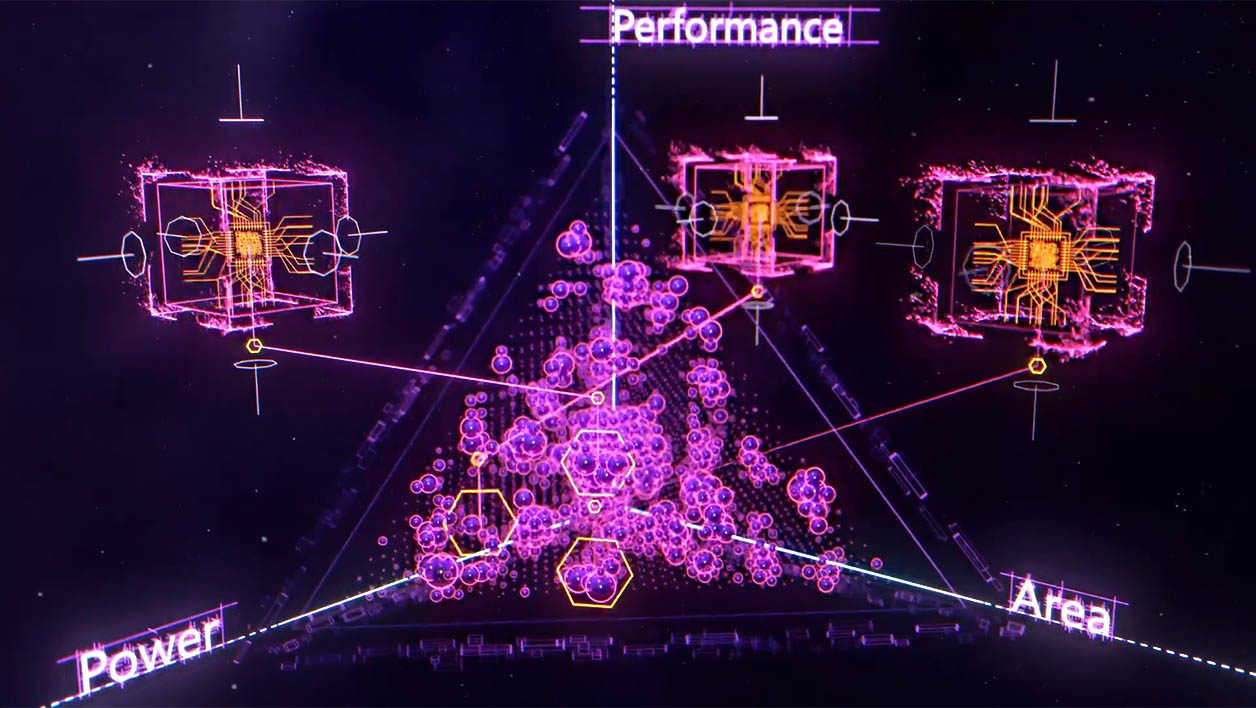

Synopsys et son rival Cadence – qui a annoncé un logiciel équivalent appelé Cerebrus en juillet dernier – ont développé des algorithmes capables de « tracer » le plan d’une puce en lui confiant les schémas des unités à intégrer, leurs interconnexions et la surface cible. Selon le patron de Synopsys, M. De Geus, la technologie permet « d’obtenir les mêmes résultats qu’une équipe de plusieurs experts en plusieurs mois, en à peine quelques semaines ».

Si les humains sont toujours bien aux commandes de la création des différents blocs d’une puce, l’IA pourrait donc rapidement prendre sa place dans une étape clé de sa création.

Source : Ars Technica

👉🏻 Suivez l’actualité tech en temps réel : ajoutez 01net à vos sources sur Google, et abonnez-vous à notre canal WhatsApp.