Alors que la production de puces gravées en 7 nm n’est pas encore pleinement lancée et le développement du process en 5 nm est à peine finalisé, Samsung publie déjà les premiers documents techniques de son procédé en 3 nm ! Si l’annonce participe d’une guerre de chiffres et de communication avec son rival TSMC, le procédé en 3 nm est intéressant car il marque une étape supplémentaire dans la miniaturisation des processeurs qui animent smartphones et ordinateurs.

Un changement structurel

Si le passage de la finesse de gravure à 7 nm implique un changement de longueur d’onde – la lithogravure est désormais réalisée par rayonnement ultraviolet extrême (EUVL) –, certains éléments de la conception des circuits reposaient jusqu’ici sur des briques d’ancienne génération (FinFET).

Le procédé 3 nm que Samsung a présenté à ses partenaires lors du Samsung Foundry Forum qui se tient en ce moment à Santa Clara en Californie passe à une étape supérieure. Le fondeur coréen a en effet présenté une nouvelle structure de conception des « gates » (portes) des transistors qui permet de tirer pleinement partie du potentiel de la gravure EUVL.

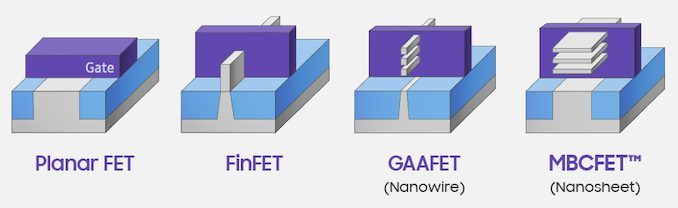

Depuis une décennie, les transistors des processeurs offre une structure dite FinFET (Fin Field Effect Transistor, transistor à effet de champ à ailette), une conception qui a eu un impact important sur la réduction de la taille des circuits, mais qui montre aujourd’hui ses limites.

L’annonce de Samsung tourne autour d’une nouvelle conception des « gates » sous la forme de nano-feuillets (nano-sheets) qui permet d’empiler les canaux de manière verticale et non plus horizontale. Ce procédé basé sur un nom barbare – gate-all-around – peut être décliné de plusieurs façons et s’appelle, en version Samsung, Multi-Bridge Channel FET ou MBCFET (encore une appellation barbare).

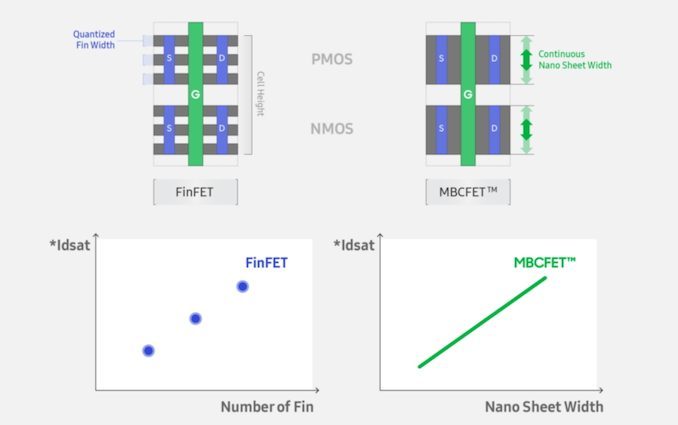

De manière sommaire, la technique de fabrication de Samsung permet non seulement d’augmenter la densité – grâce au procédé 3 nm – mais par rapport au FinFET, le procédé MBCFET offre aussi une plus grande souplesse de personnalisation des puces.

Quand le FinFET offre un choix limité de paramétrages, le procédé MBCFET permet de faire varier de manière linéaire la largeur des canaux. L’intérêt étant de pouvoir produire une puce aux petits oignons selon les besoins des clients : des canaux plus larges pour les puces hautes performances, des canaux moins larges pour des puces à basse consommation.

Si Samsung et les entreprises qui pourraient faire appel à ses services (Qualcomm, Nvidia, etc.) travaillent de concert pour lancer la production en 3 nm, l’arrivée des premières puces est pour 2021… au mieux.

Pour l’heure, Samsung n’a fourni que la première version de son kit de design produit – il n’est qu’en version 0.1 ! – et il s’agit moins d’un guide de production validé que d’un état de l’art et de la recherche.

Il faudra attendre que Samsung lance la production en 5 nm d’ici 12 à 18 mois pour savoir, selon les rendements, si le fondeur coréen arrivera bel et bien à tenir le calendrier annoncé pour le 3 nm. Mais l’annonce permet à Samsung de reprendre le leadership psychologique face à TSMC, de faire étalage de son savoir-faire… et d’enfoncer le clou face à Intel, bloqué à 10-11 nm.

Source : AnandTech

👉🏻 Suivez l’actualité tech en temps réel : ajoutez 01net à vos sources sur Google, et abonnez-vous à notre canal WhatsApp.