L’ère des transistors FinFET touche à sa fin, avec l’avènement des GaaFET. Mais avant même que ces nouveaux transistors n’arrivent en masse, IBM et Samsung ont déjà préparé l’étape d’après avec les Vertical Transport Field Effect Transistors ou VTFET. Des transistors qui ajoutent une dimension verticale à la production des puces.

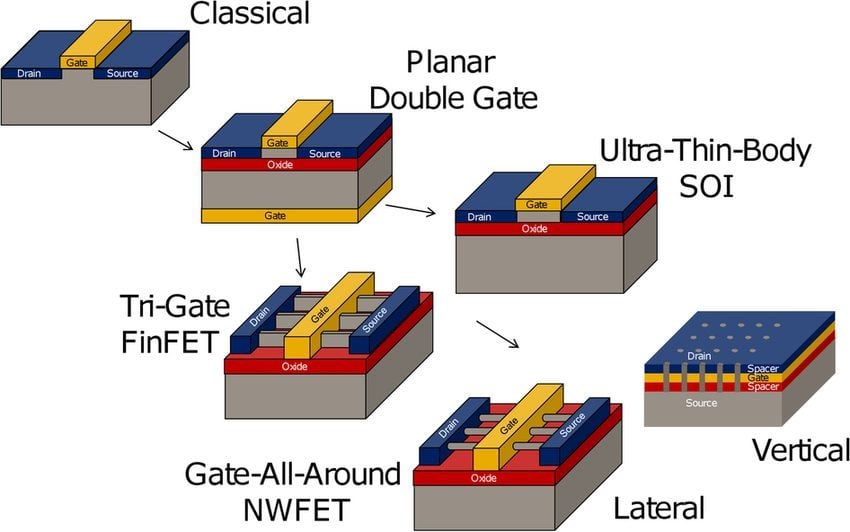

Revenons en arrière : au début, les transistors micro- puis nanométriques étaient « planaires », c’est-à-dire étendu bêtement à plat (planar). La technologie à ailettes (« fin » en anglais) dite FinFET popularisée par Intel est, depuis une décennie, le standard de facto. Une technologie qui a permis de grandement augmenter la densité au mm² et l’efficacité des circuits.

Et surtout une technologie fiable : même les dernières puces d’AMD, Apple, Intel ou Samsung utilisent cette structure en attendant que les « Gate All Arround » ou (GaaFET) et leurs évolutions, les Nanosheet (Samsung) et autres Nanoribbon (Intel) ne les remplacent.

Lire aussi : Intel dévoile ses pistes technologiques pour prolonger la loi de Moore après 2025

Encore plus performants tant en termes de densité que sur le plan électrique, les GaaFET ne sont pas encore industrialisés et devraient arriver d’ici à deux ans. Mais comme les « planar » et les « FinFET », les transistors « GaaFET » sont conçus sur deux axes, x et y. Et ne font circuler le courant qu’horizontalement.

Les VTFET d’IBM et Samsung eux, apportent la verticalité, le z. Si l’américain et le coréen ont été avares en détails, ils affichent cependant des promesses de poids : cette nouvelle structure de transistor permettrait, au choix, soit de doubler les performantes – mais lesquelles, fréquence ou densité logique ? – soit de diminuer la consommation énergétique de la puce de 85%.

Même si les deux géants des semi-conducteurs doublaient la note – ce qui n’est pas dans les habitudes d’IBM – rien que 50% de gains énergétiques ou de puissance seraient énormes dans un contexte où pour l’heure, seuls les changements de nodes (finesse de gravure) apportent des bénéfices à deux chiffres.

Si vous êtes plus habitués à lire des nouvelles concernant TSMC, Samsung ou Intel dans les informations relatives à la production de puce c’est normal, mais incomplet : si IBM a depuis longtemps lâché la fabrication de PC et la production de puce en masse (architecture Power pour Apple et Nintendo par exemple), l’américain est pourtant en pointe dans la fab. C’est lui qui a produit les premières puces en 2 nm de l’histoire.

Lire aussi : IBM grave la première puce en 2 nm de l’histoire… et Intel pourrait bien en profiter

Car IBM reste un champion de la recherche fondamentale et de la r&d. Et se sont ses ingénieurs IBM qui accompagnent Samsung BM dans l’industrialisation du procédé 5 nm EUV.

À découvrir aussi en vidéo :

L’annonce des VTFET est donc tout sauf un mensonge marketing. Mais il reste à voir comment les deux géants vont réussir à industrialiser le procédé, partie la plus sensible pour l’avènement d’une technologie.

👉🏻 Suivez l’actualité tech en temps réel : ajoutez 01net à vos sources sur Google, et abonnez-vous à notre canal WhatsApp.