En avril 2012, Li-Shiuan Peh, professeure associée en ingénierie électrique et science informatique au MIT, présentait avec ses collègues des recherches sur sa vision des processeurs de demain. Des puces capables de contourner le problème structurel des CPU actuels en adoptant une méthode de communication similaire à celle observée sur un réseau, d’où leur nom : « network on chip ». Des puces capables de multiplier les cœurs sans que cela n’implique d’engorgement des échanges internes, des puces qui sont du coup bien plus rapides et bien plus économes en énergie. Une approche « révolutionnaire » dans l’univers des processeurs.

L’arrêt du bus

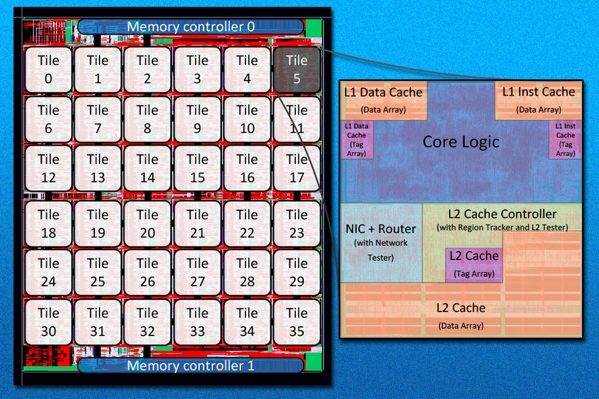

Deux ans et quelques mois plus tard, le 23 juin dernier, la même Li-Shiuan Peh a profité d’un symposium international sur l’architecture des ordinateurs pour dévoiler un processeur à 36 cœurs qui « ressemble à un petit Internet ». Chaque cœur est doté d’un routeur dont l’objectif est de permettre de contourner le traditionnel bus tout en maintenant une cohérence du contenu du cache. Il faut comprendre par là qu’il est nécessaire de s’assurer que les informations stockées localement dans chaque cœur sont identiques.

Contourner l’obstacle

Dans un processeur classique, le bus relie chaque cœur et quand un cœur a besoin d’une information, il se voit garantir l’accès exclusif au bus, chaque cœur attendant gentiment son tour et surveillant les communications de ses congénères, grâce à un protocole appelé snoopy, pour maintenir à jour leur cache.

Avec un processeur network-on-chip, chaque coeur est connecté directement à ceux qui sont à côté de lui. Ce qui induit deux effets positifs directs. Tout d’abord, qu’il est facile et très rapide d’accéder aux informations qui sont présentes dans les cœurs voisins. Ensuite, qu’il est toujours possible d’accéder à un cœur « physiquement » éloigné grâce à différents chemins. Comme pour Internet, si un des chemins est ralenti ou congestionné, il est possible d’en emprunter un autre.

En revanche, cette multiplication des voies de communication complexifie les échanges puisque qu’un cœur n’est jamais sûr d’avoir la dernière version du cache d’un autre cœur. Pour résoudre ce problème, les ingénieurs du MIT ont créé un système de hiérarchisation temporaire des priorités entre les différents cores. Une approche qui résout de nombreux points d’achoppements sur la voie du network-on-chip et devrait permettre que cette technologie soit adoptée par l’industrie.

Une voie prometteuse

Pour Todd Austin, professeur en ingénierie électrique et science informatique à l’université du Michigan : « Un des défis des universitaires est de convaincre l’industrie que leurs idées sont pratiques et utiles » indiquait-il à l’annonce de ce nouveau processeur. Les chercheurs du MIT « ont adopté le meilleur approche pour démontrer cela, de par le fait qu’ils sont fabriqué une puce qui fonctionne. Je serais surpris si ces technologies ne trouvaient pas leur chemin dans des produits commerciaux », concluait-il.

Pour l’instant, la puce va subir des tests sous forme de prototype. D’abord avec une version de Linux modifiée pour fonctionner avec 36 cœurs et des applications réelles pour s’assurer que les projections théoriques du groupe de chercheurs sont fondées.

Un autre élément devrait assurer l’épanouissement de ces processeurs. L’équipe du professeur Li-Shiuan Peh devrait en effet mettre à disposition ses schémas de conception au format open source Verilog.

A lire aussi :

Des chercheurs ont créé le premier ordinateur qui utilise des nanotubes de carbone – 01/10/2013

Source :

MIT

👉🏻 Suivez l’actualité tech en temps réel : ajoutez 01net à vos sources sur Google, et abonnez-vous à notre canal WhatsApp.