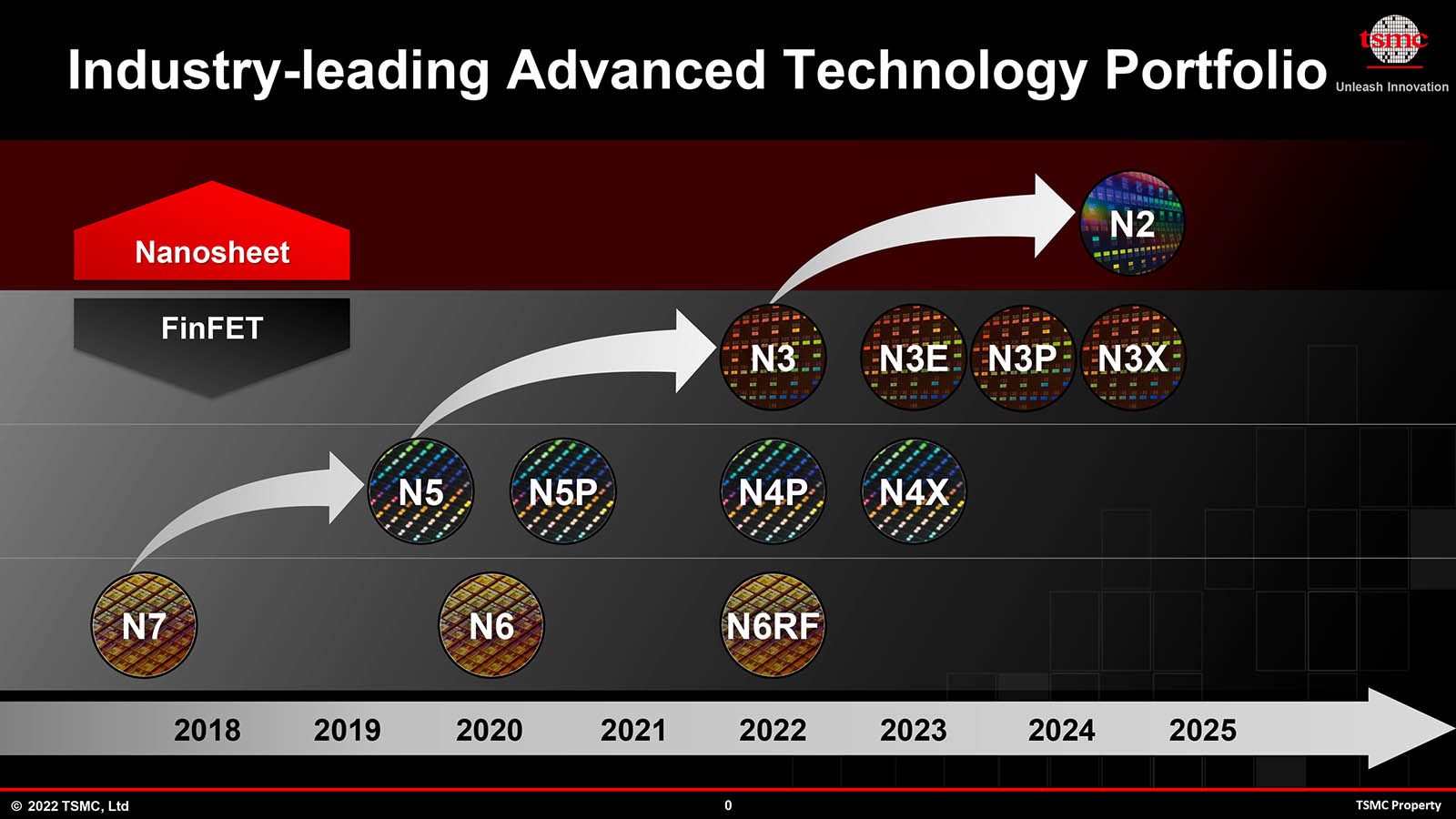

Prévue pour 2025 par le champion des puces TSMC, la gravure en 2 nm est une étape importante dans la course effrénée du monde des semi-conducteurs. Alors qu’on espérait à peine atteindre les 5 nm il y a seulement quelques années, non seulement on grave déjà en 4 nm en 2022, mais en plus la feuille de route pour le 3 nm est bouclée et le 2 nm prépare son industrialisation.

Un 2 nm appelé N2 chez le taïwanais TSMC qui apporte avec lui non seulement des améliorations attendues en matière de consommation énergétique et d’augmentation des performances, mais surtout une nouvelle architecture des transistors qui devrait être celle de la prochaine décennie.

Plus économes en énergie (mais montée en puissance modérée)

La gravure en 2 nm ne permet pas tant d’augmenter la densité de transistors – 10 % de plus par rapport à du 2 nm (N3E) – que de réduire la consommation énergétique. De manière drastique : la baisse oscillerait entre 25 et 30 % à performances égales. Ce qui est évidemment une excellente nouvelle, notamment pour les smartphones et toutes les puces embarquées.

À l’inverse, le procédé permet de gagner de la puissance par rapport au NE3… mais pas autant qu’on imaginerait. Oui, sur le papier, passer de 3 nanomètres à 2 nanomètres semble être une réduction de 33 % de la taille des circuits. Soit proche des 25-30% de l’économie d’énergie. Mais le N2 n’ajoute pas 33% de transistors en plus. Car un processeur n’est pas uniquement constitué de cette partie dite « logique », il contient aussi de la mémoire et des éléments analogiques.

Et ceux deux éléments (SRAM et composants analogiques liés au contrôle du courant) ne se réduisent plus aussi bien que par le passé. TSMC communique ici sur un exemple de puce comprenant 50% de partie logique – la seule qui profite pleinement de cette réduction de la taille des transistors – mais aussi 30% de mémoire SRAM et 20% d’éléments analogiques.

Dans les faits, TSMC table sur seulement 10% de densité de transistors en plus par rapport au 3 nm. Alors comment diable peut-on obtenir 25-30% de baisse de consommation ? Grâce à de nouveaux types de transistors.

Au revoir FinFETs, bonjour GAAFETs

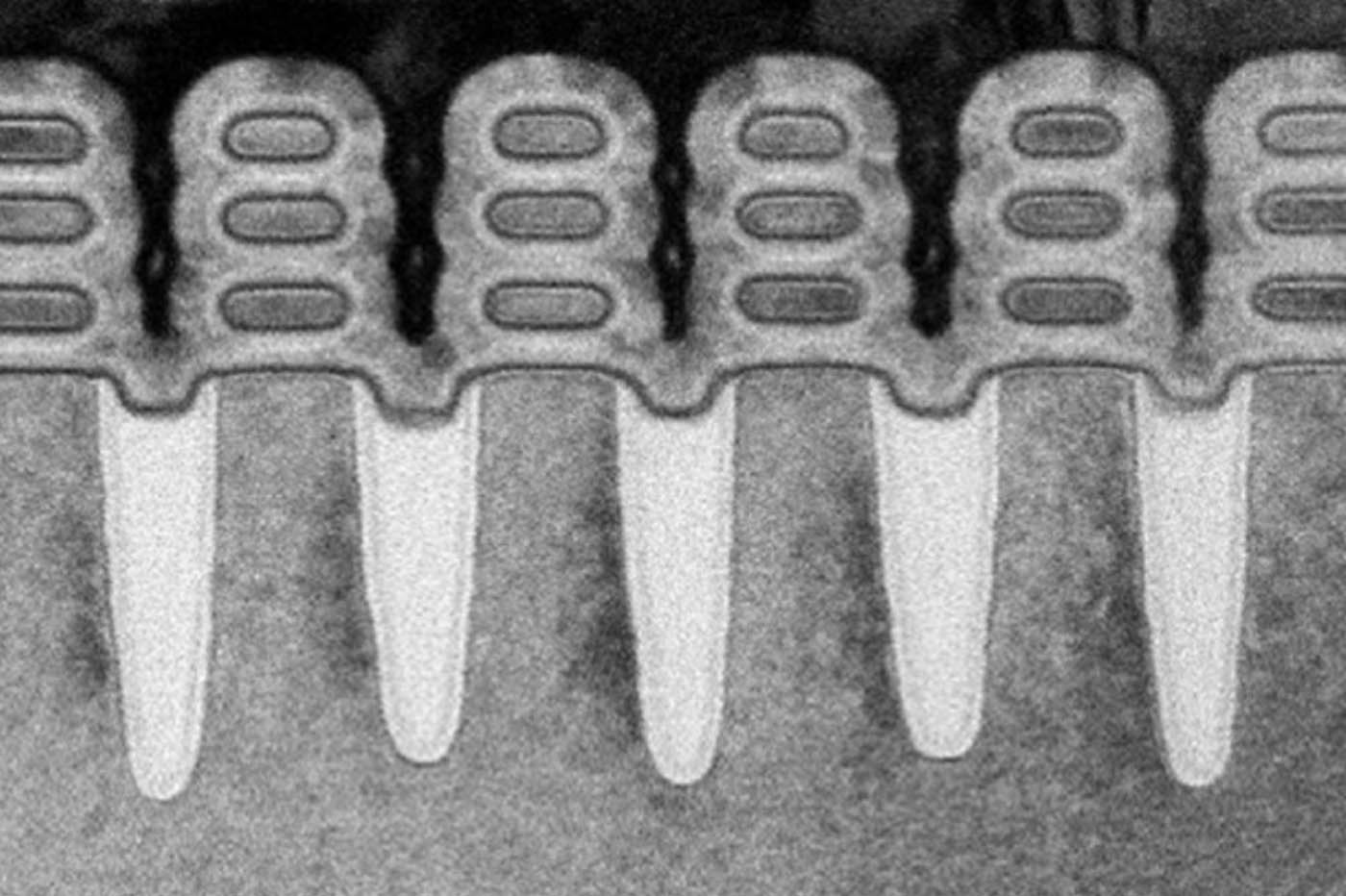

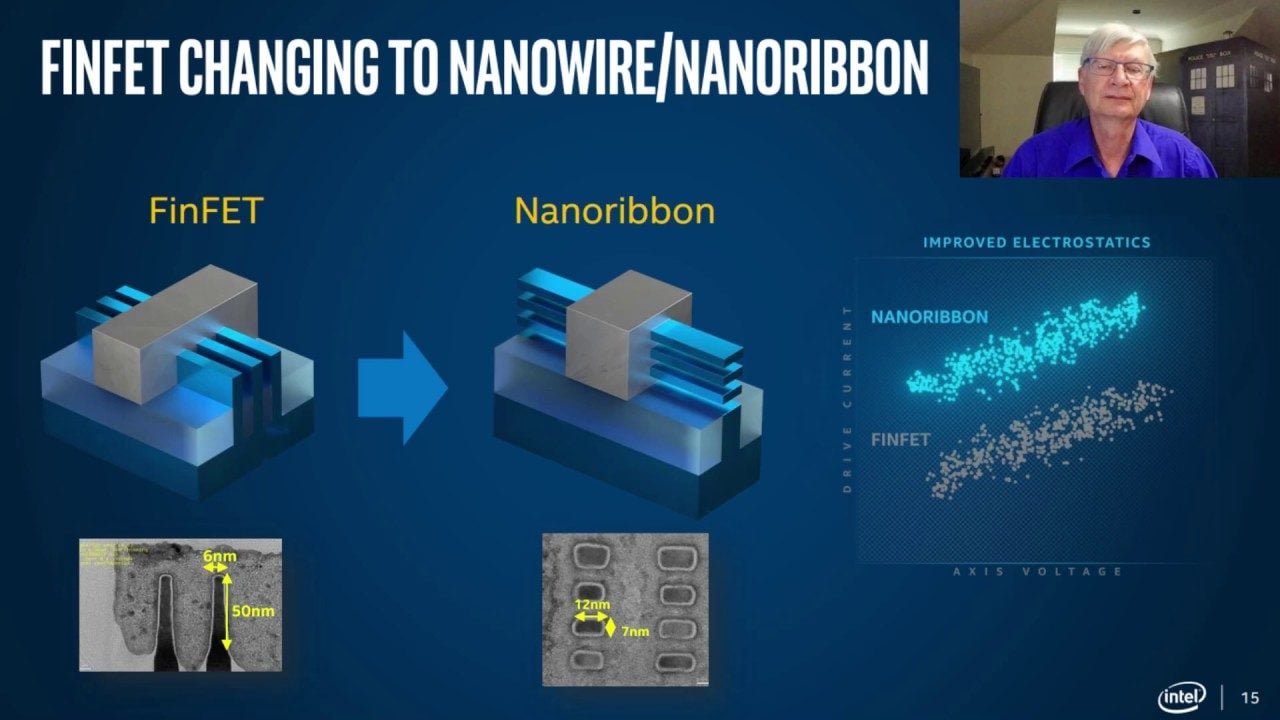

Comme nous vous en avons déjà parlé, TSMC a réussi à faire vivre les transistors « classiques » de type FinFET pendant très longtemps. Mais cette structure de transistors à ailettes (« fin » en anglais signifie aileron, nageoire) a fait son temps et c’est un autre type de transistors qui va prendre le relais. Appelé nanosheet par TSMC, nanoribbon par Intel, c’est l’appellation GAAFET de Samsung qui est la plus parlante. Car elle explique bien que ces « nano-couches/nano-fils » passent dans une porte logique qui les entoure complètement – Gate All Around Field Effect Transistor.

Et c’est la nature de cette structure, qui isole bien mieux les circuits les uns des autres, qui permet de limiter la consommation énergétique. Le fait que les circuits soient totalement entourés permet de mieux gérer les fuites d’énergie, d’avoir plus de latitude dans le voltage, etc. La seule difficulté de ce procédé conceptualité en 1988 par Toshiba était l’industrialisation. Et TSMC semble être le premier à en récolter les fruits pour ses futurs clients – qui a parlé d’Apple ?

👉🏻 Suivez l’actualité tech en temps réel : ajoutez 01net à vos sources sur Google, et abonnez-vous à notre canal WhatsApp.

Source : AnandTech