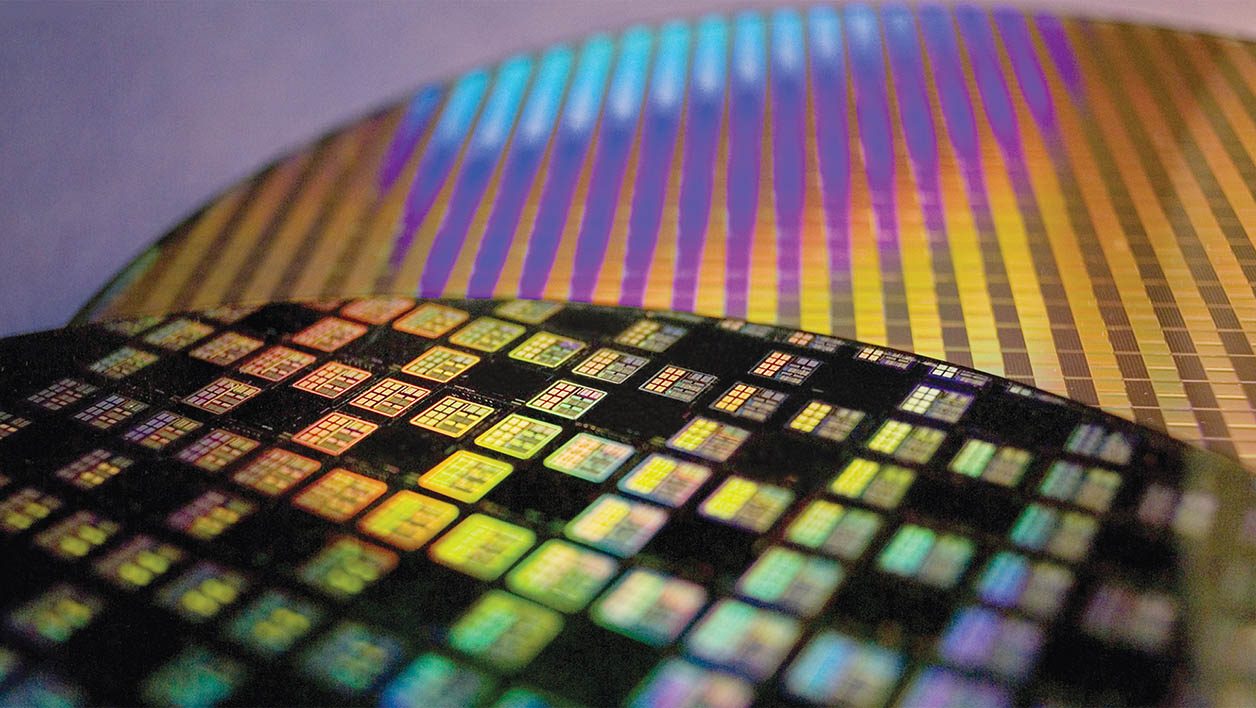

Tous les voyants de la feuille de route technologique de TSMC (Taiwan Semiconductor Manufacturing Company) sont au vert. Le champion mondial de la finesse de gravure et de la production en masse de composants de pointe affiche un plan technologique implacable.

Une amélioration du processus en 5 nm

Déjà maître de la gravure EUV avec un procédé en 5 nm bien plus performant que celui de son concurrent Samsung (le N5 affiche 170 millions de transistors par mm² contre seulement 125 millions chez Samsung), le Taïwanais ne cesse de progresser.

Ainsi, un nouveau nœud de production appelé N5P va va être rapidement disponible en production de masse. Evolution du N5 normal (gravure EUV, en 5 nm FinFET), ce procédé promet une réduction de 10% de la consommation énergétique ou une hausse de fréquence de 5%. Des gains « gratuits » puisqu’ils ne requièrent aucun travail ou presque sur le design N5 originel.

Vers les 4 et 3 nm

Suivra ensuite le nœud N4, une gravure EUV en 4 nm, qui rentrera en production à risque en fin d’année et en production de masse en 2022. TSMC ne s’engage pas encore sur les gains effectifs, car ils n’ont pas encore été mesurés avec précision.

Mais là encore, le fondeur promet « une migration très facile du N5 et N5P vers des designs N4 ». Comprendre que pour les concepteurs de puces que sont Apple, AMD ou Qualcomm, le travail d’adaptation de l’architecture pour les lignes de productions sera sans douleur.

Même son de cloche pour le process N3, en 3 nm donc, et majoritairement en EUV. Un procédé qui devrait être au point d’ici la fin de l’année en mode « risque », mais dont la production de masse ne devrait débuter que dans la seconde partie de 2022.

Les gains promis sont de taille : à complexité égale de puce, les gains de performances (fréquences) pourraient aller de 10% à 15%. Ou abaisser la consommation énergétique de 25% à 30%.

Cette course à la finesse et aux capacités de production – 80% des 100 milliards que TSMC a prévu d’investir dans les trois ans concernent l’ouverture de nouvelles lignes de production ! – s’explique par le fait que « les clients s’emparent du 5 nm et 3 nm encore plus vite qu’à l’époque du 7 nm. La demande est tellement forte que nous devons préparer notre capacité de production », dixit l’entreprise.

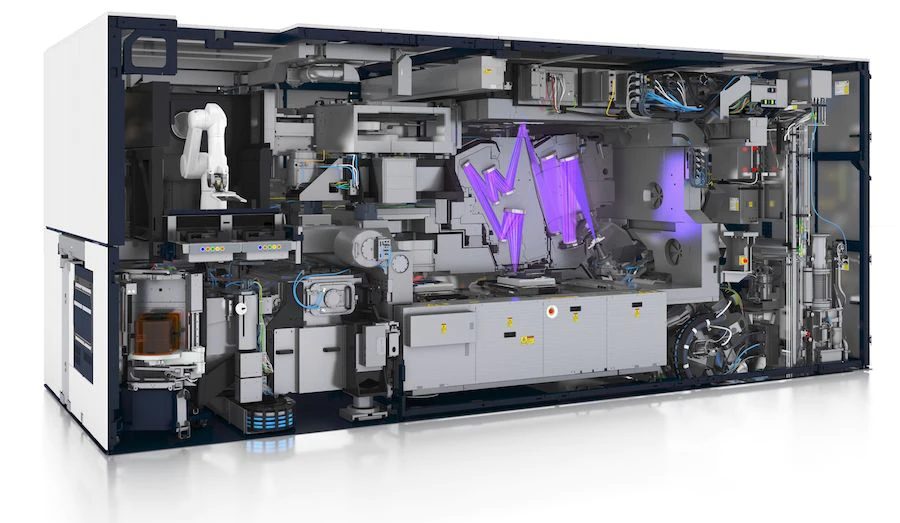

Cette adoption est autant le fait de la finesse de gravure en elle-même que de la qualité des rendements de l’entreprise. Ils sont basés sur un mélange de technologie de pointe – la gravure EUV – et de designs éprouvés, notamment en matière de transistors.

Grâce au FinFET, des rendements au-delà des espérances

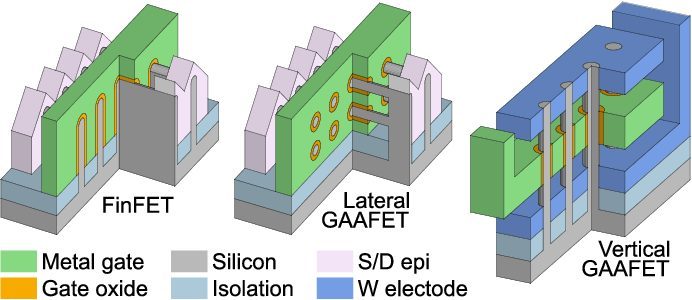

TSMC a réussi avec une stratégie technologique diamétralement opposée à celle qu’a suivi Intel ces cinq dernières années. L’Américain a mis de côté la gravure EUV pour se concentrer sur des technologies de conception des puces et d’agencement des transistors (Foveros, EMIB, SuperFIN et GAAFET).

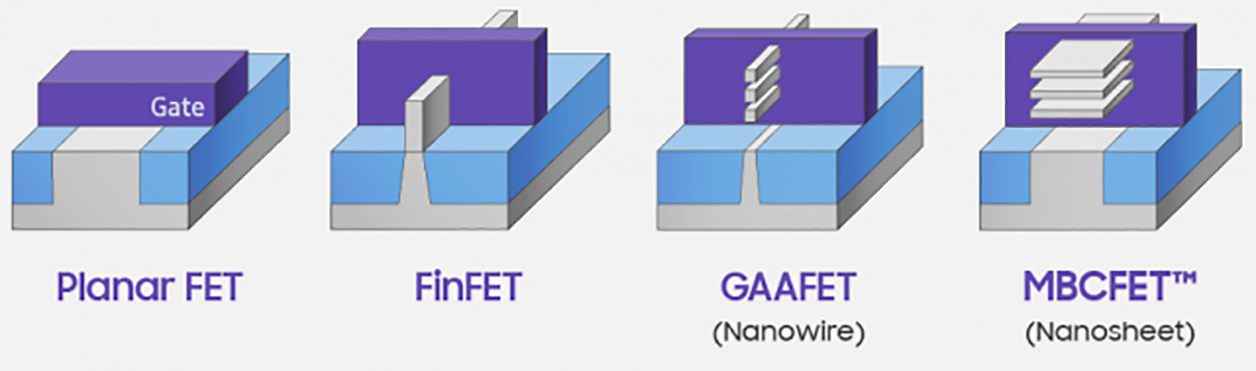

A contrario, le Taïwanais a continué d’utiliser les transistors « classiques », dits à effet de champ à ailettes (Fin Field-Effect Transistor ou FinFET), pour tout miser sur le procédé EUV et les améliorations de la finesse des procédés. Une procédure moins subtile dans l’approche, mais qui colle à l’identité de TSMC. La société doit séduire des clients avec des procédés plus simples et moins risqués pour ses clients.

Des clients qui connaissent bien les transistors FinFET. Le principe de ces transistors à ailettes a été conceptualisé en 1989, et la production de masse pour les processeurs date des années 2010. Il s’agissait du procédé 22 nm d’Intel – qui régnait alors en maître sur le monde des semi-conducteurs.

L’avantage pour TSMC de s’appuyer sur ces « vieux » transistors c’est que cela facilite le travail de ses clients. Puisque le Taïwanais arrive à améliorer sans cesse la finesse de gravure et propose des rendements de qualité, il n’est pas si important que la conception des transistors ne soit pas à la pointe comme ce que proposent Intel (SuperFIN) ou Samsung (GAAFET).

Il est largement plus important pour les équipes d’Apple, d’AMD, de MediaTek et autres de ne pas avoir trop d’effort de design et de mise en production (mêmes logiciels, mêmes procédés de validation) pour mettre sur le marché de nouvelles puces toujours plus puissantes.

A découvrir aussi en vidéo :

TSMC a donc bien joué en pensant avant tout à ses clients, qui n’ont pas à gérer la partie difficile – la gravure en ultraviolets-extrêmes, que le Taïwanais maîtrise désormais comme personne. Ce qui ne veut pas dire que l’entreprise fasse une croix sur les nouveaux transistors de type GAAFET qui sont toujours dans sa feuille de route.

Mais ils apparaîtront sur la feuille de route « post-N3 », c’est-à-dire à partir de 2 nm. Puisque la finesse de gravure sera alors encore plus difficile à réduire, l’entreprise ambitionne de s’appuyer à ce moment-là sur les « supers » transistors pour continuer d’améliorer les performances de ses clients.

Et tenter de rester le champion incontesté de la gravure.

Source : AnandTech

🔴 Pour ne manquer aucune actualité de 01net, suivez-nous sur Google Actualités et WhatsApp.