Adieu Pentium, vive Core ! Tel pourrait être le slogan d’Intel, qui a complètement revu l’architecture interne de ses puces pour sa nouvelle génération de processeurs. Oubliée la course effrénée à la fréquence qui avait fait les

beaux jours des différentes séries de Pentium depuis 1993.En raison des problèmes physiques qu’elle avait fini par poser (consommation électrique et dissipation thermique), Intel s’était retrouvé dans une impasse technologique en ne parvenant pas à atteindre la barrière symbolique des

4 GHz avec le Pentium 4. Désormais, les gigahertz ont moins d’importance et c’est sur l’optimisation de l’organisation interne des processeurs que les ingénieurs concentrent leurs efforts.A l’instar d’IBM et d’AMD, son éternel concurrent, Intel a ainsi misé sur le principe du multic?”ur, autrement dit, de la puce contenant plusieurs processeurs (on parle de c?”ur). Pour le moment, seuls des processeurs à deux

c?”urs (double c?”ur) sont proposés pour les ordinateurs grand public, mais des versions à quatre c?”urs devraient arriver d’ici début 2007.Le premier processeur double c?”ur Intel, baptisé Pentium D, a débarqué à la mi-2006. Conçu à la va-vite, à partir de c?”urs de Pentium 4, pour contrer l’Athlon 64 X2 d’AMD, il a vite été abandonné au profit du

processeur Core Duo, plus performant car bâti sur des c?”urs de Pentium M (développé pour la plate-forme Centrino). Mais c’est avec l’architecture Core qu’Intel innove vraiment.Déclinée sur toute la nouvelle gamme de processeurs Intel, sous la dénomination commerciale Core 2 Duo (série E6xxx pour les PC de bureau, séries T7xxxx et T5xxx pour les portables et Xeon 51xx pour les serveurs), elle introduit

plusieurs techniques visant à optimiser les performances et la consommation électrique (voir ci-dessus).Et le travail des ingénieurs d’Intel a payé. Selon les premiers tests effectués, les Core 2 Duo seraient, à fréquence égale, 20 % plus performants que les Core Duo actuels…

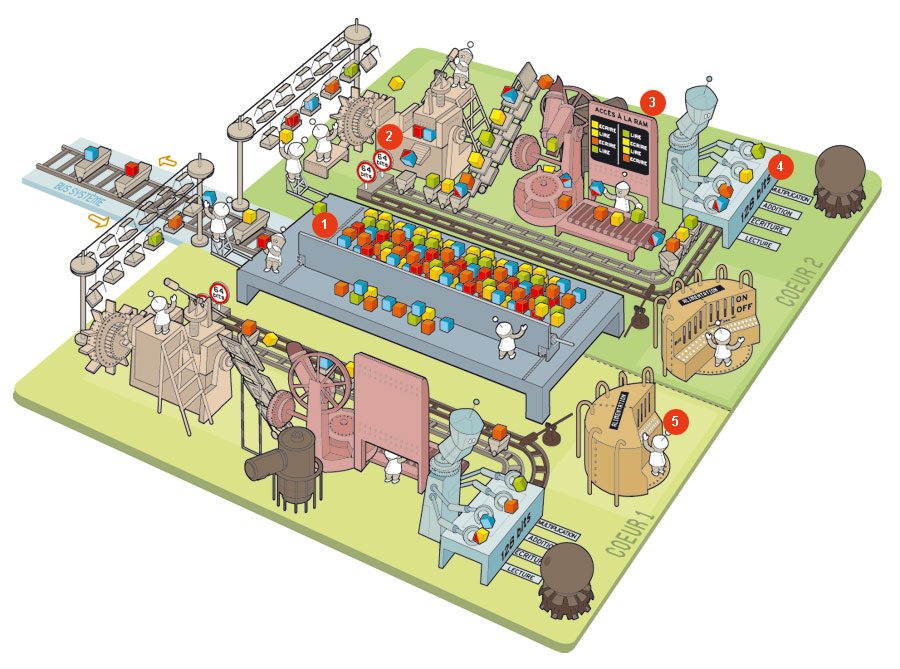

1. Les c?”urs se partagent la mémoire cache

Intégrée au processeur, la mémoire cache de niveau 2 est une mémoire vive ultrarapide qui sert d’intermédiaire entre les c?”urs et le bus système. Pour éviter les allers-retours avec la mémoire vive, elle stocke temporairement les

données et les instructions dont les c?”urs peuvent avoir besoin, en anticipant certaines demandes. Dans les puces double c?”ur de première génération d’Intel, chaque c?”ur possédait son propre cache.Avec l’architecture Core, cette mémoire est unifiée et partagée ‘ dynamiquement ‘ entre les deux c?”urs : chaque c?”ur peut s’en octroyer à volonté une portion de taille variable pour y stocker les

informations qu’il veut garder sous la main. S’il en a besoin, l’autre c?”ur peut accéder directement à ces données, sans passer par le bus système externe.

2. Certaines micro-instructions sont fusionnées

Les instructions provenant du système d’exploitation sont transformées en une suite de micro-instructions (des commandes élémentaires adaptées aux unités de traitement du processeur). Quand c’est possible, l’architecture Core regroupe

deux micro-instructions en une seule, afin de réduire le nombre total d’opérations à exécuter par les unités de traitement. Un mécanisme de fusion qui revêt un intérêt évident quand on sait qu’un programme peut générer plusieurs milliards de

micro-instructions…

3. Les accès à la mémoire sont optimisés

Sur les précédents processeurs Intel, les instructions de lecture et d’écriture en mémoire vive (Ram) étaient exécutées scrupuleusement dans l’ordre où elles apparaissaient. Du coup, un processus A ayant besoin de lire en mémoire

pouvait être interrompu temporairement, en attendant qu’un processus B ait fini d’y écrire ses données.Et ce, même si les données de ces deux processus étaient totalement indépendantes ! L’architecture Core est capable de découpler ces opérations dès lors qu’elles ne concernent pas les mêmes données, ce qui favorise les

traitements en parallèle.

4. Les données de 128 bits sont traitées en parallèle

Les instructions destinées aux traitements multimédias (de type SSE2 ou SSE3) manipulent des données codées sur 128 bits. Comme les bus véhiculant les données à l’intérieur de chaque c?”ur étaient limités à 64 bits sur les

précédents processeurs Intel, il fallait deux cycles pour traiter une seule de ces instructions.En exploitant un bus de données de 128 bits, l’architecture Core se contente d’un seul cycle par instructions. Et comme chaque c?”ur dispose de quatre unités spécialisées dans ce type de traitements, il peut exécuter quatre

instructions en parallèle sur un seul cycle !

5. Les modules inutilisés sont désactivés

Pour limiter la consommation électrique, certains sous-ensembles des c?”urs peuvent être désactivés momentanément, à la volée, quand ils ne sont pas utilisés (par exemple, les unités de traitement sur les nombres réels si les

traitements en cours portent sur des nombres entiers). En outre, les bus de données de 128 bits sont dédoublés en deux bus de 64 bits ; un bus de 64 bits peut ainsi être désactivé en l’absence de données sur 128 bits.Enfin, le processeur est capable de renseigner certains composants de la carte mère (régulateur de voltage, ventilateurs, etc.) sur son besoin en énergie du moment.

🔴 Pour ne manquer aucune actualité de 01net, suivez-nous sur Google Actualités et WhatsApp.